“슈퍼칩 한계론”…웨이퍼 엔진, AI 데이터센터 판도 바꾼다

AI 처리 성능을 좌우해 온 슈퍼칩이 근본적인 공정 한계에 부닥치면서, 웨이퍼 스케일 엔진 등 신개념 집적 반도체가 AI 데이터센터의 구도를 뒤흔들고 있다. 최근 엔비디아가 선보인 블랙웰 슈퍼칩조차 2080억개의 트랜지스터를 품었음에도, 물리적인 '레티클 한계'에 가로막혀 추가 확장이 쉽지 않다는 지적이 나온다. 기존 반도체 집적 방식은 네덜란드 ASML의 익스트림 머신 등 첨단 EUV(극자외선) 노광 장비가 지원하지만, 한 번 조사할 수 있는 면적이 최대 800제곱밀리미터로 제한된다. 이러한 레티클 크기는 곧 칩의 한계를 결정하고, 많은 연산을 위해 슈퍼칩들을 복잡하게 연결해야 했다.

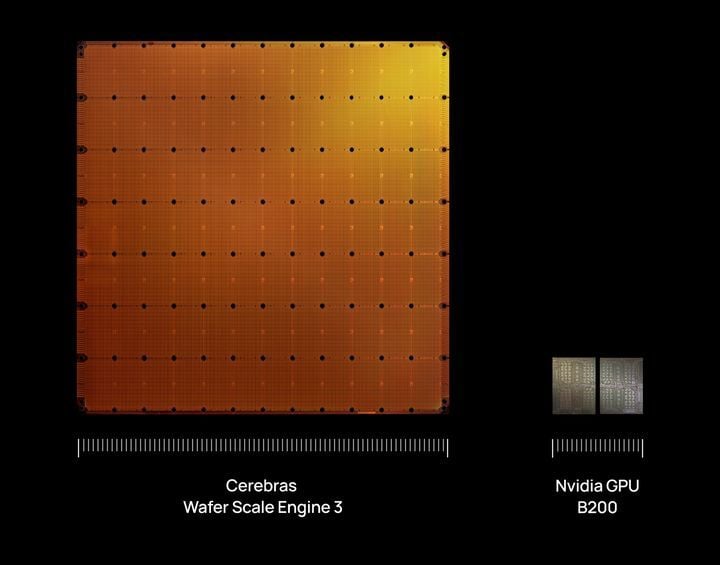

특히 데이터센터에서는 개별 슈퍼칩을 와이어와 광섬유로 연결하면서 발생하는 통신 오버헤드가 점점 부담이 되고 있다. 이 기술적 병목을 해결할 차세대 대안으로 부상한 것이 웨이퍼 스케일 엔진(WSE)이다. 미국 세레브라스는 WSE-3 엔진을 발표하며, 전체 데이터센터의 기능을 단일 웨이퍼에 통합했다. WSE-3는 약 4조 개의 트랜지스터로, 기존 블랙웰 대비 집적도는 14배, 메모리 대역폭은 약 7000배 수준에 이른다는 설명이다. 전통적인 칩 구조와 달리, 메모리를 별도 소자 없이 웨이퍼에 직접 통합함으로써 내부 통신 병목을 최소화했다. 실제로 세레브라스는 웨이퍼 엔진 16개를 묶어 6조4000억개의 트랜지스터가 들어간 초소형 데이터센터 박스를 구현했다.

동시에, 멀티빔 등에서는 ‘다중 전자빔 리소그라피’라는 신형 장비를 개발, 기존 레티클 한계를 기술적으로 우회할 수 있다고 알렸다. 멀티빔은 8인치 웨이퍼에서도 초미세 회로 패턴을 직접 새기는 방식을 검증 중이다. 이처럼 글로벌 데이터센터 시장은 전통 슈퍼칩 집적의 한계와 웨이퍼 통합 엔진의 새 가능성이 첨예하게 맞서는 양상이다.

미국을 비롯, 중국도 메모리와 연산 일체형 대형 웨이퍼 구조 개발에 연구비를 집중하고 있다. 시장 전문가들은 ‘웨이퍼 엔진’이 AI 기반 초대규모 연산 환경의 전환점을 찍을 산업 요인으로 언급한다. 한편 집적도 혁신 외에, 웨이퍼 크기 엔진의 상용화는 데이터센터의 에너지와 공간 효율 문제, 기존 배치/서버 표준 체계와의 통합 여부 등 규제 및 산업 구조 변동성과도 맞닿아 있다.

업계에서는 “슈퍼칩의 한계 극복이 AI 데이터센터 경쟁의 새로운 서막이 될 가능성도 있다”고 진단한다. 산업계는 웨이퍼 스케일 엔진이 실제 시장에 안착할지, 기존 반도체 및 데이터 인프라와 어떻게 접목될지 예의주시하고 있다.